物理性質比較

第一代半導體自身性能受限,不適合在高溫、高壓、高頻、高功率等領域使用。

化合物半導體通常指晶態無機化合物半導體,即是指由兩種或兩種以上元素以確定的原子配比形成的化合物,並具有高電子遷移率、禁帶寬度高等特性,能在高溫、高壓、高頻等環境中使用。

化合物半導體通常指晶態無機化合物半導體,即是指由兩種或兩種以上元素以確定的原子配比形成的化合物,並具有高電子遷移率、禁帶寬度高等特性,能在高溫、高壓、高頻等環境中使用。

Si

第一代

GaAs

第二代

GaN

第三代

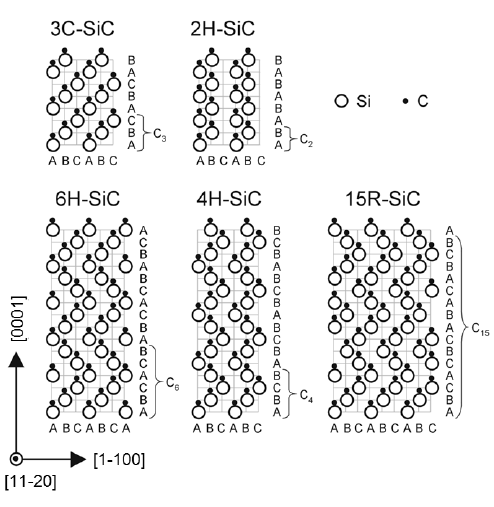

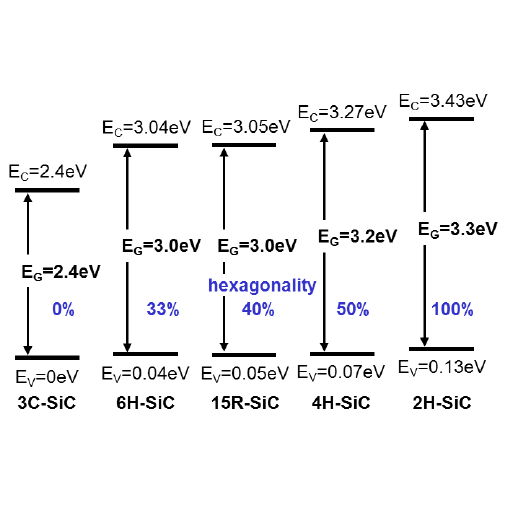

4H-SiC

4H-碳化矽

6H-SiC

6H-碳化矽

3C-SiC

3C-碳化矽

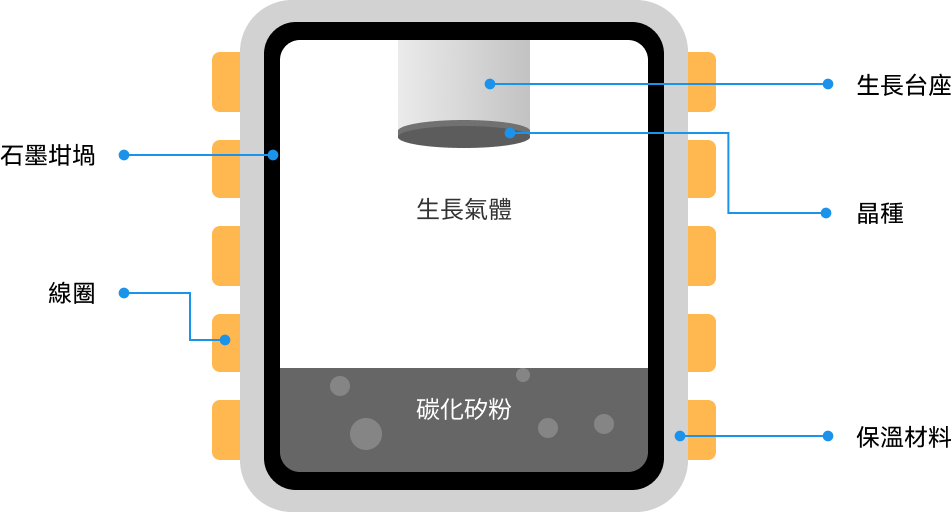

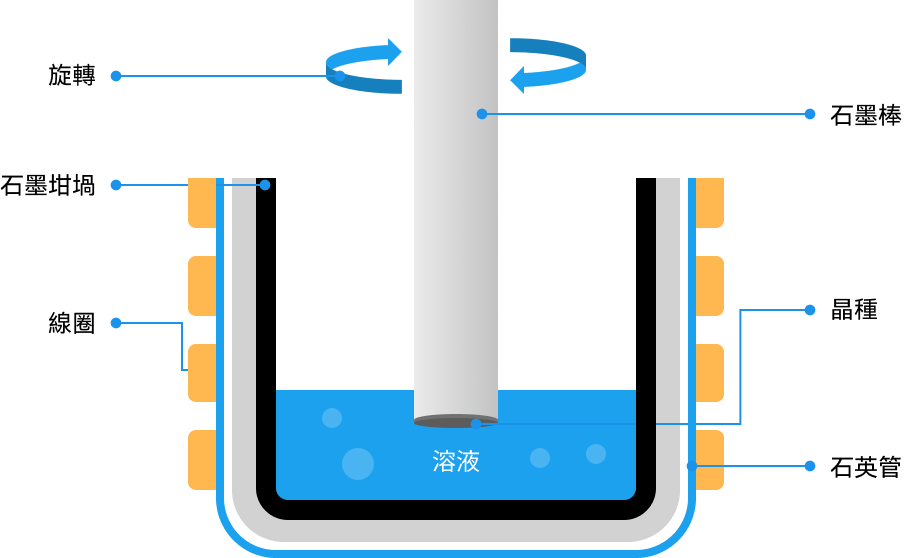

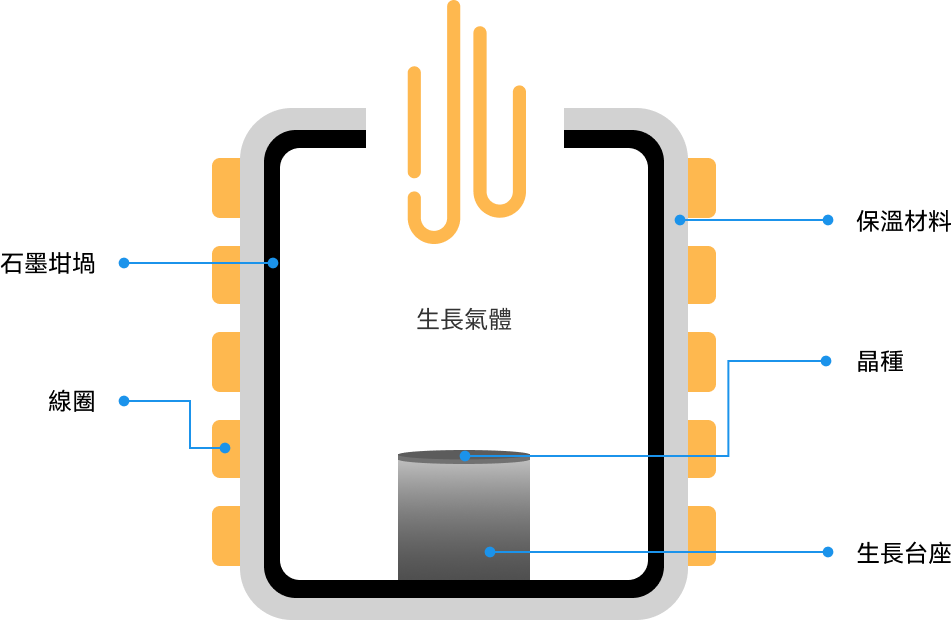

第三代—碳化矽